# Algorithm Implementation in FPGAs Demonstrated Through Neural Network Inversion on the SRC-6e

A Thesis Submitted to the Graduate Faculty of

**Baylor University**

in Partial Fulfillment of the

Requirements for the Degree

of

Masters of Science

By

Paul D. Reynolds

Waco, Texas

May 2005

# TABLE OF CONTENTS

| List of Figures                                | V    |

|------------------------------------------------|------|

| List of Tables                                 | vi   |

| Acknowledgments                                | vii  |

| Dedication                                     | viii |

| Chapter One                                    | 1    |

| Introduction                                   | 1    |

| Chapter Two.                                   | 2    |

| The SRC-6e Reconfigurable Computer             | 2    |

| Hardware Architecture                          | 2    |

| SRC-6e Development Environment                 | 4    |

| Hardware Description Language Implementation   | 5    |

| Chapter Three                                  | 7    |

| The Acoustic Algorithm                         | 7    |

| The Neural Network                             | 7    |

| Particle Swarm Optimitzation                   | 8    |

| Chapter Four                                   | 10   |

| Neural Network Accuracy and Sigmoid            | 10   |

| From Floating to Fixed Point                   | 11   |

| The Sigmoid Approximation                      | 14   |

| Look Up Table Implementation                   | 14   |

| Shift-add Implementation                       | 15   |

| The Neural Network                             | 18   |

| Taylor Segments Approximation                  | 22   |

| Comparison Summary                             | 24   |

| Chapter Five                                   | 27   |

| Neural Network Implementations                 | 27   |

| Serial Implementation                          | 27   |

| Parallel Node Implementation                   | 28   |

| Parallel Input Implementation                  | 32   |

| Conclusions on Neural Network Implementations  | 33   |

| Chapter Six.                                   | 35   |

| Particle Swarm Implementation.                 | 35   |

| Deterministic Particle Swarm                   | 35   |

| Randomization                                  | 37   |

| Linear Feedback Shift Register                 | 37   |

| Squared Decimal Implementation                 | 40   |

| Particle Swarm Randomness Results              | 42   |

| Conclusions on Particle Swarm Implementation   | 42   |

| Chapter Seven                                  | 45   |

| Algorithm Speedup through FPGA Implementations | 45   |

| Parallel-able                                  | 45   |

| Pipeline-able                         | 47  |

|---------------------------------------|-----|

| Memory Transfer                       | 49  |

| Speed Ratio                           | 50  |

| Appendices                            | 52  |

| Appendix A                            | 53  |

| Parallel Input Network and Swarm Code | 53  |

| Main.c                                | 53  |

| Appendix B                            | 60  |

| Parallel Input Network and Swarm Code | 60  |

| Makefile                              | 60  |

| Apeendix C                            | 62  |

| Parallel Input Network and Swarm Code | 62  |

| Swarm.mc                              | 62  |

| Appendix D                            | 69  |

| Parallel Input Network and Swarm Code | 69  |

| Fitness.mc                            | 69  |

| Appendix E                            | 74  |

| Parallel Input Network and Swarm Code | 74  |

| Blkbox.v                              | 74  |

| Appendix F                            | 78  |

| Parallel Input Network and Swarm Code | 78  |

| Macros.inf                            | 78  |

| Appendix G                            | 82  |

| Parallel Input Network and Swarm Code | 82  |

| Moveit.vhd                            | 82  |

| Appendix H                            | 85  |

| Parallel Input Network and Swarm Code | 85  |

| Squash.vhd                            | 85  |

| Bibliography                          | 123 |

# LIST OF FIGURES

| Figure 1:  | The SRC-6e Block Diagram                                              | 3  |

|------------|-----------------------------------------------------------------------|----|

| Figure 2:  | Accuracy Sweep of Squashing Function                                  | 12 |

| Figure 3:  | Accuracy Sweep of Weights                                             | 13 |

| Figure 4:  | Accuracy Sweep of all Fractional Bits                                 | 13 |

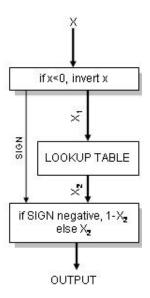

| Figure 5:  | The Block Diagram for a Lookup Table Implementation of the Sigmoid.   | 15 |

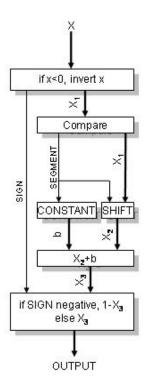

| Figure 6:  | The Block Diagram for a Shift-Add Implementation of the Sigmoid       | 16 |

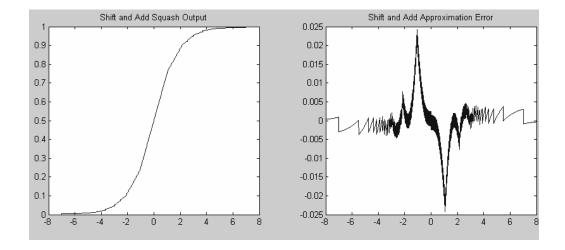

| Figure 7:  | VHDL Approximation of Shift and Add Squashing Function                | 17 |

| Figure 8:  | Comparison of Shift-Add FPGA Output with Real Output                  | 17 |

| Figure 9:  | A Piecewise Linear Approximation of the Sigmoid                       | 18 |

| Figure 10: | VHDL Approximation of CORDIC Squashing Function                       | 20 |

| Figure 11: | The Block Diagram for a CORDIC Implementation of the Sigmoid          | 21 |

|            | Comparison of CORDIC FPGA Output and Real Output                      | 22 |

| Figure 13: | The Block Diagram for a Taylor Series Implementation of the Sigmoid   | 23 |

| Figure 14: | VHDL Approximation                                                    | 24 |

| Figure 15: | Comparison of FPGA Output with Real Output                            | 24 |

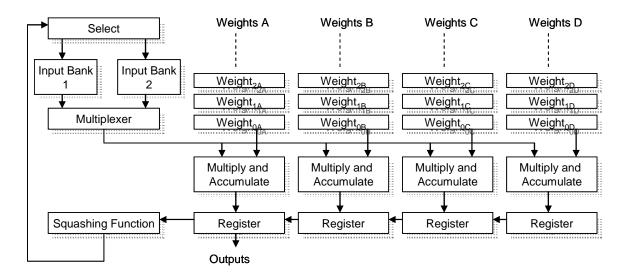

| Figure 16: | The Block Diagram for the Serial Implementation of a Neural Network   | 28 |

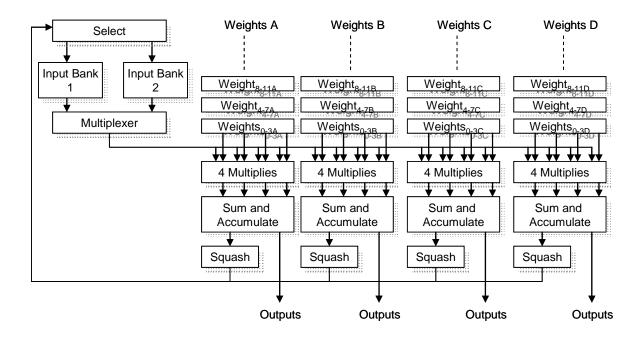

| Figure 17: | The Parallel Node Implementation with Four Parallel Nodes             | 30 |

| Figure 18: | Parallel Node Implementation with Sixteen Multiplies                  | 31 |

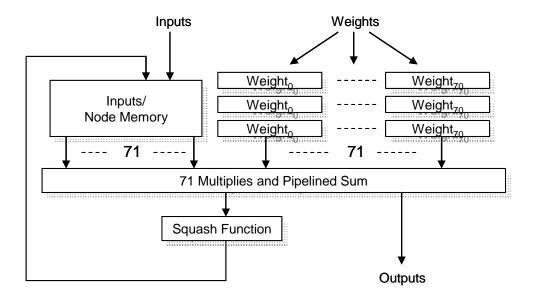

| Figure 19: | A Simplified Block Diagram of a Node Parallel Implementation          | 33 |

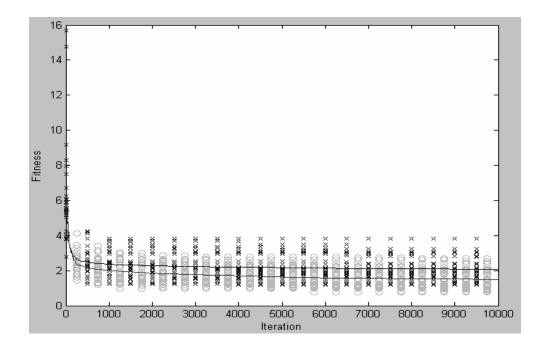

| Figure 20: | Particle Swarm with and without Randomness                            | 36 |

| Figure 21: | Deterministic Particle Swarm Block Diagram.                           | 37 |

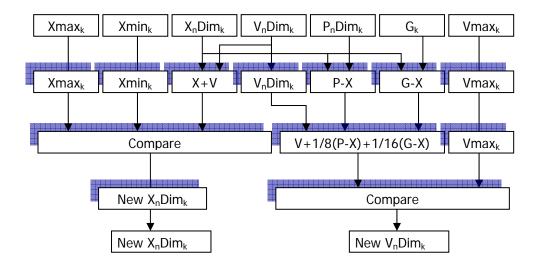

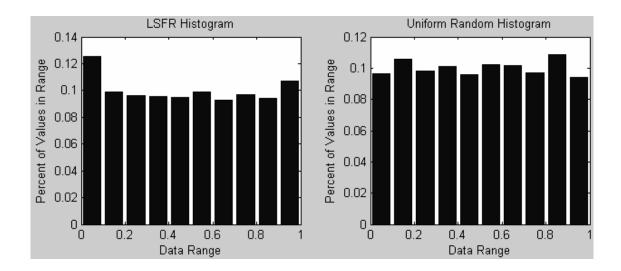

| Figure 22: | Histograms for a LFSR Implementation and a Uniform Random Variable    | 39 |

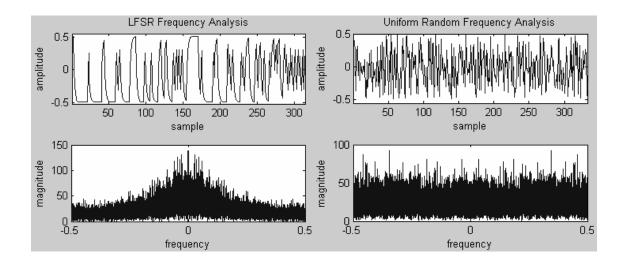

| Figure 23: | Output Streams and Frequency Spectra f or a LFSR Implementation and a |    |

|            | Uniform Random Variable.                                              | 39 |

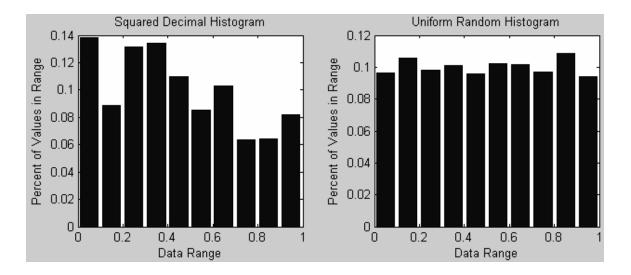

| Figure 24: | Histograms for a Squared Decimal Implementation and a Uniform Random  | ì  |

|            | Variable                                                              | 41 |

| Figure 25: | Output Streams and Frequency Spectra f or a Squared Decimal           |    |

|            | Implementation and a Uniform Random Variable                          | 41 |

| Figure 26: | Particle Swarm Results Maximizing a Specified Area                    | 43 |

| Figure 27: | Particle Swarm Results Maximizing a Specified Area                    | 44 |

# LIST OF TABLES

| Table 1: | Segments Used for the Shift-Add Approximation | 16 |

|----------|-----------------------------------------------|----|

| Table 2: | CORDIC Initializing Segments                  | 21 |

|          | Taylor Series Segments and Coefficients       | 23 |

| Table 4: | A Comparison of Approximations                | 25 |

#### **ACKNOWLEDGMENTS**

I would like to thank Dr. Russell Duren and Dr. Robert Marks for providing me with this topic to work on as well as for helping me think of ideas for some portions of the problem. I'd also like to thank Dan Zulaica and David Caliga for helping me to figure out some errors in my programming and giving me hints on how to use the computer. I would also like to thank Burton Ottewell for doing some initial work on the SRC-6e from which I could learn.

# **DEDICATION**

To my parents, who let me graduate free of debt

#### **CHAPTER ONE**

#### Introduction

The hardware implementation of algorithms can be a difficult process. An algorithm takes a given input and produces an output based on several calculations. Unlike state machines, an input can only produce one output, and a design could be implemented as purely combinational logic. This, however, would be very complex and likely have several timing issues. It is much more effective and organized to divide an algorithm into several clocked segments. This way, the correct data will arrive at components at the proper time and the arrival of a valid output is highly predictable.

Algorithms also tend to be too large for every calculation to be performed by different hardware components. Implementation of large algorithms requires that many components be reused during computation and therefore some method of control. State machines are not required; usually a simple series of counters is sufficient.

The example presented is of neural network inversion. This thesis begins with a brief introduction to the hardware and programming environment. Chapter three introduces the algorithm being implemented as well as the problem background. Chapters four, five and six describe implementations of the three inversion subalgorithms as well as the adaptations required for hardware. The final chapter explains how hardware implementations are in effective decreasing algorithm computation time. The appendices present the code for the final implementation of hardware neural network inversion.

#### **CHAPTER TWO**

## The SRC-6e Reconfigurable Computer

The SRC-6e Reconfigurable Computer, from here on referred to as the SRC-6e, is a specialized system designed for the implementation of code in reconfigurable hardware. The system contains two reconfigurable chips accessible by core processors. The chips are programmed using languages tailored specifically for the system.

The SRC-6e has previously been used for applications by the Naval Postgraduate School in implementing CORDIC functions [1, 2], certain RADAR applications [3], as well as with Triple DES [4]. A group in Washington, D.C. used the SRC-6e for work with cryptosystems [5].

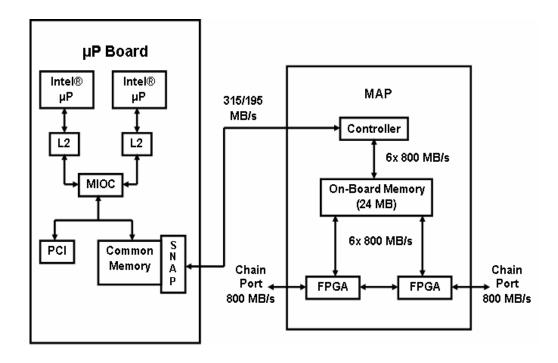

#### *Hardware Architecture*

The SRC-6e contains two Pentium 3 microprocessors running at one gigahertz and two Xilinx XC2V6000 field programmable gate arrays(FPGA) running at one hundred megahertz. The XC2V6000 contains pre-configured logic blocks in order to simplify the implementation of some designs. Each XC2V6000 contains 144 eighteen-bit multiplier blocks and 144 eighteen-kilobit random memory access blocks. In addition to pre-defined logic, each chip has approximately six million user-definable logic gates [6].

In order for the hardware to be useful, it must be able to read and write to memory used by the main processors. For this purpose, there are six on-board memory blocks. Each block contains four megabytes of memory, accessible by either FPGA. The processors can access this memory through an on-board controller. The controller can

move data between the on-board memory and the common, processor accessible memory. In a typical program, the processor instructs the controller to load data to be manipulated or analyzed; this data is then loaded into the on-board memory where it is accessed by the reconfigurable hardware. Once computations are complete, the results are stored in on-board memory and the controller transfers them back to common memory for use by the microprocessors. A block diagram of the SRC-6e is shown in Figure 1.

Figure 1: The SRC-6e Block Diagram. The SRC-6e contains two Pentium 3 microprocessors and two Xilinx XC2V6000 FPGAs [7].

If both available FPGAs are utilized, they are arranged in a master-slave relationship, with one FPGA controlling the other. The master FPGA permits the slave access to read and write to specific memory blocks and controls when the slave begins calculations. Along with the memory blocks, the master and slave can communicate

directly through three sixty-four bit ports. Once both FPGAs have completed calculations, the master regains control of all six memory blocks and the controller copies the results to common memory [7].

#### SRC-6e Development Environment

The SRC-6e has its own development environment and uses several programming languages for design implementation. The SRC-6e runs a Linux operating system and is controlled remotely via x-windows or a command line interface. At the highest level of an implementation, the main program is written in the standard C language and executes on the Intel processors. The main program executes as with any other platform, and the command line and console can be used for user input or data display. From the main program, the reconfigurable hardware is accessed in the same manner as a function. The hardware function handles the necessary data transfers and execution on the hardware.

The hardware functionality is programmed in a modified C or FORTRAN, which is translated by the SRC-6e compiler into Verilog code, which is then synthesized and encoded into FPGA bit streams using standard FPGA design tools. The hardware generation process is hidden from the programmer who simply issues a make command to generate the compiled and synthesized program.

The high level languages can be used exclusively by themselves or along with functions written in one of two standard hardware description languages, VHDL or Verilog. Hardware description languages are used when more control is desired over the FPGA circuitry. The design for the example used in this thesis was coded using a combination of C and VHDL. It is also possible to use intellectual property cores in a design. The core can be called from the VHDL or Verilog code and the precompiled core

file uploaded to the SRC-6e. The compiler will properly connect the design. This method is used for the division operation shown in the CORDIC portion of the example.

#### Hardware Description Language Implementation

Hardware description languages are especially useful to gain more control of parallel processes as well as to circumvent some of the idiosyncrasies of the higher level programming languages. For example, the compiler will often add latency to loops during compilation for implementation. This can be difficult to fix in the higher level languages, though the solution may be quite obvious at the hardware description level. One particularly frustrating peculiarity is the implementation of multipliers. For all multiply commands, the complier requires three multipliers to be used, though typically one is sufficient. The compiler's multipliers also are intended for integers. For a fixed point design, the decimal point must be moved after every multiply. This is much easier to implement at the hardware description level.

To use hardware description languages, a module is written in either VHDL or Verilog and then is called as a function from the C or FORTRAN hardware code. In order for the complier to know how the higher level programming languages will communicate with the function, two additional files must be created. In the files, the function inputs and outputs are listed along with their order and sizes as well as the nature of the function. The compiler needs to know when it is able to send inputs and when to retrieve outputs. The programmer must define whether the function is stateful, external, pipelined, or periodic as well as its latency as described in the SRC C reference guide.

In some instances, such as the following problem presented, some of the highlevel language idiosyncrasies force much of the logic to be performed in the hardware description languages. However, the resulting function will not fit into any of the predefined function characteristics. In order to circumvent this problem, the function can be defined as functional with a pipelined structure and placed in a loop. In order for the technique to work, the loop must be programmed so that the compiler will not add latency. The latency is assigned as the time from when the last input enters to the time the last output calculation is finished. Then, from the high level language side, if the number of inputs differs from the number of outputs, pseudo-inputs can be used to fill the extra clocks if there are more outputs than inputs or additional outputs can be ignored if the reverse is true.

#### CHAPTER THREE

#### The Acoustic Algorithm

Given a set of sonar system parameters and environmental parameters, the acoustical state of an underwater environment can be predicted by computationally intensive computer models. It is desirable to be able to perform an inversion on the system: given the state of the underwater environment and some fixed parameters, determine the other input parameters to achieve optimal sonar performance. Inversion is performed by testing many different sets of the variable input parameters and choosing the set that mostly closely matches the desired acoustical state. In order to perform the inversion in real time, the computation time of the model must be small and the number of sets of unknown parameters tested kept at a minimum.

Previous work with the acoustic model has been performed by the University of Washington and the Jet Propulsions Laboratory. Some of their work can be found in [8], [9], and [10].

#### The Neural Network

In order to decrease the calculation time of the forward computation, an artificial neural network was trained using data from the acoustic model. The network has a 27-40-50-70-1200 architecture, with the 27 inputs corresponding to the sonar system and environmental parameters and the 1200 outputs corresponding to the acoustic state of water at points on an 80 by 15 grid [11].

The three hidden layer network greatly decreases forward computation time, from a few minutes using the acoustic model, to few milliseconds. Though this speed is acceptable for real-time forward calculations, it is too slow to produce a real-time inversion. By using a parallel FPGA implementation, computation time can be decreased enough to make real-time inversion possible.

#### Particle Swarm Optimization

In order to minimize the number of sets of unknown parameters tested, a particle swarm optimization is used. Particle swarm optimization employs several agents exploring a multi-dimensional search space to maximize a given fitness function. As the agents traverse the space, they have tendencies to return to their own previous best locations as well as to the best location of the group. The tendency is based on the distance from the best locations and some uniform randomness. The update equations are:

$$X[k+1] = X[k] + A_0V[k]$$

$$V[k+1] = V[k] + C_1R_1(P - X[k]) + C_2R_2(G - X[k])$$

The next location, X[k+1], and next velocity, V[k+1] of each agent are determined using the following: X[k], the current location; V[k], the current velocity;  $A_0$ , an update constant controlling the resolution of movement;  $C_1$  and  $C_2$ , bias coefficients;  $R_1$  and  $R_2$ , uniform random variables between 0 and 1; P, the personal best fitness location and G, the group best fitness location.

For the above neural network inversion, the fitness function is defined as the sum of the differences in pixels in the calculated acoustical state and the desired state. A smaller sum is considered to have a higher fitness. To prove that the inversion method is

viable, a known achievable set of outputs is used as the desired state. If the inputs found by the inversion produce approximately the same set of outputs, then the method can be used to invert a set of desired outputs that lie outside the achievable set with confidence that nearly the closest attainable set is found.

Certain frequently used limits are also applied to the particle swarm. Velocity is limited to help keep particles from jumping over minimums in thin valleys. The range is also limited to keep particles from using search time to look in unrealistic areas.

#### **CHAPTER FOUR**

## Neural Network Accuracy and Sigmoid Implementation

For this inversion implementation, the master-slave relationship is used between the two FPGAs with the particle swarm optimization acting as master and the neural network fitness function acting as slave. The neural network was implemented first in order to prove feasibility of the design.

Typically, when a neural network is implemented on an FPGA, it is trained for specifically for that purpose, using powers of two weights and a lookup table or other specialized activation function [12]. However, our problem involves a computer-trained network using continuous weights and a sigmoid activation function. The problem of continuous weights is solved by rounding and using a fixed-point representation and fast multipliers built into the FPGA. This still leaves the problem of the activation function.

When the activation function is a sigmoid, it can be found using exact methods, such as a look up table or a CORDIC function. Another common method is to use a simple piece-wise linear approximation [13]. However, each of these methods has undesirable aspects. In order to keep the entire network internal to one chip, a lookup table is undesirable. A CORDIC function gains accuracy at the cost of latency. The piece-wise linear method, while small and quick, has limited accuracy. Our problem requires a quick, smooth activation function approximation that can approximate a sigmoid to arbitrary accuracy.

A Pentium 4 running at 1.8 gigahertz can theoretically perform the forward calculation in .116 milliseconds if it performed one calculation per clock. However, due

to memory access time and a non-dedicated processor, the actual forward calculation time is .28 milliseconds. The FPGA implementation can execute the forward calculation in under 1500 clocks. At one hundred megahertz, this translates to less than .015 milliseconds per forward calculation, a gain of eighteen over the Pentium 4.

#### From Floating to Fixed Point

In order to conserve chip space and computational intensity, short fixed-point representations of numbers are desired. In the aforementioned neural network, all internal calculations are of the same order of magnitude, lending the solution to a fixed-point representation. The inputs and outputs are a few orders of magnitude greater than the network calculations. However, they are consistent among themselves and can also be stored in a fixed-point representation. The corresponding input and output weights can be scaled to account for the difference, so that all layer calculations appear to be of the same order of magnitude.

To define the representation, two parameters must be specified, the length of the integer bits and the length of the fractional bits. Based on computer simulations, the sigmoid input range is from negative fifty to eighty-five. This range requires a minimum of eight bits, one sign bit and seven magnitude bits. Also based on computer simulations, an accuracy of at least 1/128<sup>th</sup>, or seven fractional bits, is desirable.

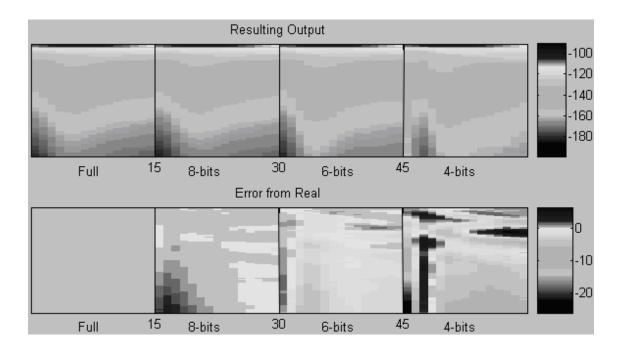

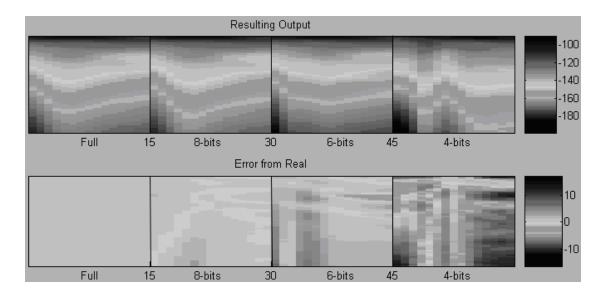

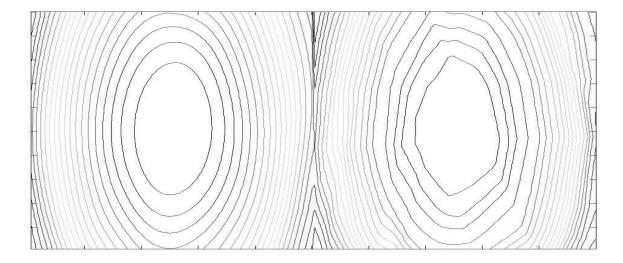

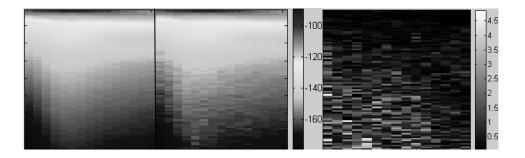

Results of the computer simulations are shown in Figure 2 through Figure 4. While all other calculations were performed at maximum accuracy, the bit accuracy of the output of the squash was varied. The result for one case is shown in Figure 2. Figure 3 shows the result of changing the bit accuracy of weights while performing all other

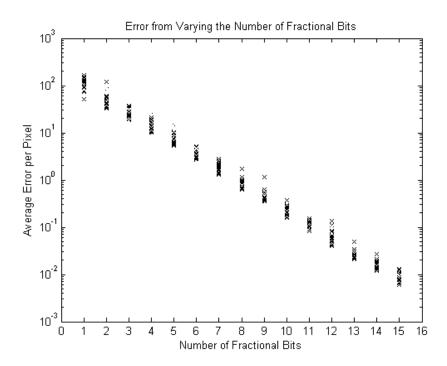

calculations at maximum accuracy. A chart of the average pixel error for one hundred different cases is shown Figure 4.

The FPGAs use six sixty-four bit busses to access the on-board memory. The sixty-four bits can be easily divided into two thirty-two bit numbers or four sixteen bit numbers. The XC2V6000 uses eighteen-bit multipliers, which makes the sixteen-bit representation desirable. Sixteen bits is sufficient according to the accuracy calculations, allowing a representation with one sign bit, seven integer bits, and eight fractional bits. Computer simulations showed that this representation averages .866 units of error per pixel. Since pixels are on the order of magnitude of hundreds, the error is typically less than one percent.

Figure 2: Accuracy Sweep of Squashing Function. Using one of the sonar problem's inputs, the image map output was calculated using an ANN with a squashing function rounded to various levels of accuracy. The input and weights maintained complete accuracy. The difference from maximum accuracy is shown under each image. From left to right, the four outputs use sixteen, eight, six and four fractional bits for the squash output.

Figure 3: Accuracy Sweep of Weights. Using one of the sonar problem's inputs, the image map output was calculated using an ANN with weights rounded to various levels of accuracy. The input and squashing function maintained complete accuracy. The difference from maximum accuracy is shown under each image. From left to right, the four outputs use sixteen, eight, six and four fractional bits for weights.

Figure 4: Accuracy Sweep of all Fractional Bits. Using one hundred sets of inputs, the average error per pixel was calculated using an ANN with all numbers rounded to various levels of bit accuracy. As expected, the error decreases logarithmically as the number of fractional bits increases.

## The Sigmoid Approximation

The familiar sigmoid – or logistic function - version of the squashing function is

$$y(x) = \frac{1}{1 + e^{-x}}$$

Detailed evaluation of the sigmoid, however, is computationally intensive on an FPGA. The sigmoid is used 160 times per neural network evaluation. Therefore, in order to implement the network on an FPGA, a small, quick, and accurate sigmoid approximation is desired.

# Look Up Table Implementation

The simplest implementation method is to use a lookup table. In order in to make a lookup table, a limited operating range must be determined. Using the nearly odd property,

$$f(-x) = 1 - f(x),$$

of the squashing function, the size of the lookup table can be decreased to half the desired range. The non-saturation range is between -8 and 8, so the look-up table only needs operate between 0 and 8. This requires three integer bits and all eight fractional bits to be used as address bits. Any numbers not in that range are considered to be in saturation and assigned an output value of 1. The resulting table has eleven address bits selecting the eight bit fractional portion, using two kilobytes of memory. The lookup table implementation of a sigmoid has a latency of three. This implementation could be undesirable since available on-chip memory may be needed for weight storage.

Figure 5: The Block Diagram for a Lookup Table Implementation of the Sigmoid.

## Shift-add Implementation

One common implementation is to use a piecewise linear approximation with many segments of

$$y = mx + b$$

If the segments are chosen wisely, the sigmoid can be calculated using only bit shifts and additions [13]. However, this method has a limited accuracy, with no possibility for improvement. At its worst, the approximation is nearly .025 off the actual value of the sigmoid.

Another problem is also present; the piecewise linear approximation is not very smooth. In computer simulations, a network work using a full accuracy sigmoid was trained using elliptical data. Then the sigmoid was replaced by the shift-add approximation. The results are shown in Figure 9. The piecewise approximation results in an undesirable piecewise approximation of the output. Further examination shows that

training with the shift-add approach also results in piecewise outputs. The shift-add implementation of the sigmoid has a latency of five.

Figure 6: The Block Diagram for a Shift-Add Implementation of the Sigmoid.

TABLE 1 SEGMENTS USED FOR THE SHIFT AND ADD APROXIMATION

| Lower Bound | Slope | Constant   |

|-------------|-------|------------|

| 7.236       | 0     | 1.0        |

| 5.846       | 1/512 | 0.984375   |

| 5.147       | 1/256 | 0.97265625 |

| 4.442       | 1/128 | 0.953125   |

| 3.724       | 1/64  | 0.91796875 |

| 2.977       | 1/32  | 0.859375   |

| 2.164       | 1/16  | 0.765625   |

| 1.065       | 1/8   | 0.6328125  |

| 0.0         | 1/4   | 0.5        |

Figure 7: VHDL Approximation of Shift and Add Squashing Function. The VHDL implementation of the shift-add squash is on the left and the error is shown on the right. The shift and add approximation of the sigmoid is nearly 3% off from the actual at its worst.

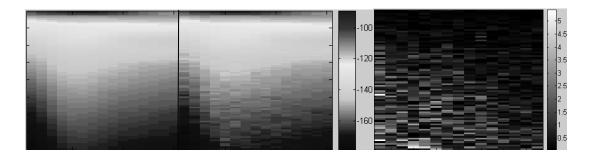

Figure 8: Comparison of Shift-Add FPGA Output with Real Output. One of the known input/output relationships was used to test the FPGA implementation. The map on the left shows a comparison of the real image and that produced by the FPGA. The absolute difference of the two images is shown in the map on the right.

Figure 9: A Piecewise Linear Approximation of the Sigmoid. A piecewise linear approximation of the sigmoid results in a piece of approximation of the original outputs.

# CORDIC Implementation

A third method to approximate a sigmoid is to use a CORDIC algorithm [14] to calculate the hyperbolic sine and cosine in order to obtain the hyperbolic tangent. The tangent can then be used in the sigmoid equivalent

$$y(x) = \frac{1}{2} \tanh \frac{x}{2} + \frac{1}{2}$$

The CORDIC algorithm works by rotating a vector by known angles until the sum of the angles is equivalent to the desired angle. CORDIC uses the properties that

$$\begin{pmatrix} \cosh(a \pm b) \\ \sinh(a \pm b) \end{pmatrix} = \begin{pmatrix} \cosh(b) & \pm \sinh(b) \\ \pm \sinh(b) & \cosh(b) \end{pmatrix} \begin{pmatrix} \cosh(a) \\ \sinh(a) \end{pmatrix}$$

With a small amount of algebra:

$$\begin{pmatrix} \cosh(a \pm b) \\ \sinh(a \pm b) \end{pmatrix} = \cosh(b) \begin{pmatrix} 1 & \pm \tanh(b) \\ \pm \tanh(b) & 1 \end{pmatrix} \begin{pmatrix} \cosh(a) \\ \sinh(a) \end{pmatrix}$$

$$\cosh(a \pm b) = \cosh(b)(\cosh(a) \pm \tanh(b) \sinh(a))$$

$$\sinh(a \pm b) = \cosh(b)(\sinh(a) \pm \tanh(b) \cosh(a))$$

By starting with the hyperbolic sine and cosine of known angle a, a desired hyperbolic sine and cosine can be calculated by applying the above equations with known b and previously calculated cosh(b) and tanh(b). The equations can be applied repeatedly with other known b's until the proper sum is reached.

By choosing tanh(b) to be negative powers of 2, such as 1/2, 1/4, 1/8, etc., all the multiplications can be executed as shifts. The cosh(b) can be found for each of the previous. The product of the cosh(b) from all iterations is found and used as an initial constant.

The most commonly used initial argument is zero, with the starting vector as (1.20744 0). However, the range of the CORDIC algorithm starting at this vector is limited to the sums of the known b's. When using tanh(b) as only powers of 2, the radius of convergence is slightly greater than 1.13.

This creates a problem with the sigmoid implementation. Using the almost odd property, the desired sigmoid range is from zero to eight. Though since the argument is divided by two, the necessary range of the hyperbolic tangent is zero to four, which is out of the convergence range.

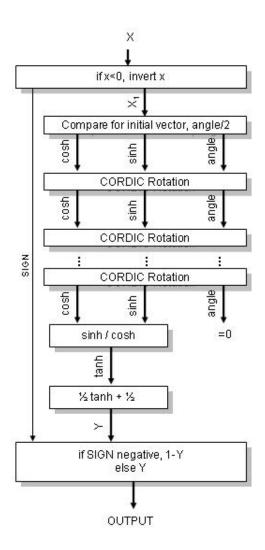

In order to get the necessary range to converge, the desired range is divided into segments the same size as the standard range. In this case, two segments were used, zero to two and two to four. Then, when a tangent needs to be found, the initial vector is

chosen based on the argument. If it the argument is in the first segment, the initial vector is chosen to be the hyperbolic cosine and sine of one multiplied by the product of the  $\cosh(b)$  and the  $\cosh(1)$ . For the second segment, the hyperbolic cosine and sine of three is used along with the product of the  $\cosh(b)$  and  $\cosh(3)$ . This way, the regions of convergence for the two segments overlap slightly and also extend beyond the desired range. If more range is necessary, more segments can be used. If a more accurate result is desired, more CORDIC rotations can be used.

Once the hyperbolic cosine and sine are found, tangent is found by division. A standard Xilinx core is used for division. Once the tangent is found, a shift of one bit is used to divide by two and one half is added to the result.

The eleven stage CORDIC algorithm and divide implementation fits into a pipeline that has a latency of 50.

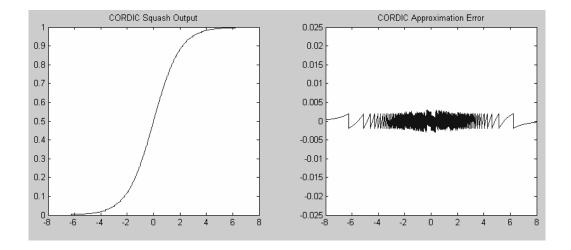

Figure 10: VHDL Approximation of CORDIC Squashing Function. The VHDL implementation of the CORDIC squash is on the left and the error is shown on the right. The approximation of the sigmoid remains within .005 for the entire range.

TABLE 2

CORDIC INITIALIZING SEGMENTS

| Segment Center | Hyperbolic Cosine | Hyperbolic Sine |

|----------------|-------------------|-----------------|

| 1              | 1.89325           | 1.419043        |

| 3              | 12.1566           | 12.09648        |

Figure 11: The Block Diagram for a CORDIC Implementation of the Sigmoid.

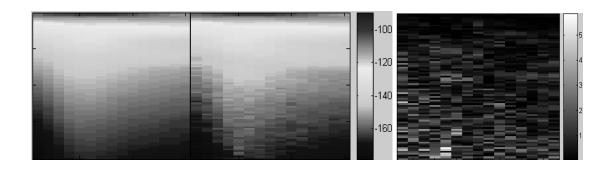

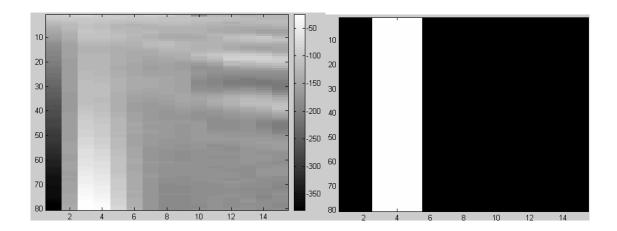

Figure 12: Comparison of CORDIC FPGA Output and Real Output. One of the known input/output relationships was used to test the FPGA implementation. The map on the left shows a comparison of the real image and that produced by the FPGA. The absolute difference of the two images is shown in the map on the right.

## Taylor Segments Approximation

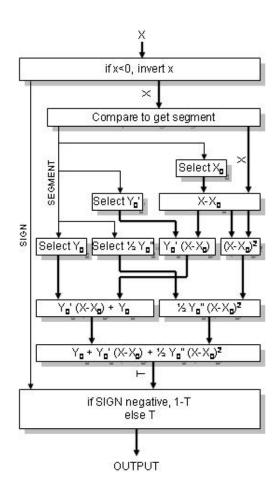

The fourth approximation examined was a Taylor series about zero, though convergence was slow. To avoid this problem, several second order segments of Taylor series about different points are used, with a general formula of

$$y(x) = -y_0''*(x - x_0)^2 + y_0'*(x - x_0) + y_0$$

Then, given the argument, the proper offset and coefficients are chosen. The accuracy of the approximation can be improved by increasing the number of segments used in the approximation. This implementation uses three multipliers, three adders, three multiplexers, and a number of comparators equivalent to the number of segments.

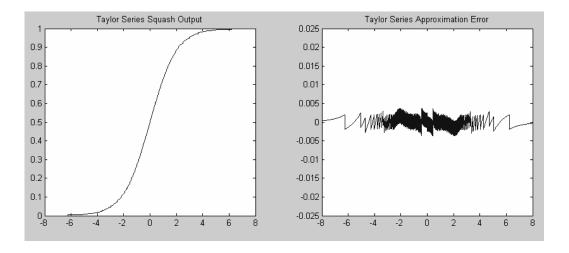

As with the other implementations, a pipelined version is desired. The pipeline is shown in Figure 13. It was expected that the pipeline would have a latency of eight. However, for multipliers on the XC2V6000 to operate at 100 MHz, a latency of two is required to complete a computation. Since there are two stages of multipliers, the total latency is ten.

TABLE 3: TAYLOR SERIES SEGMENTS AND COEFFICIENTS

| Lower Bound | $x_0$ | y <sub>0</sub> " | yo'               | уо              |

|-------------|-------|------------------|-------------------|-----------------|

| 7.293       | 0.0   | 0.0              | 0.0               | 1.0000000000000 |

| 4.771       | 6     | 0.001220703125   | 0.00244140625000  | 0.997558593750  |

| 3.317       | 4     | 0.008544921875   | 0.01757812500000  | 0.982055664063  |

| 2.482       | 2.75  | 0.024780273438   | 0.05639648437500  | 0.939941406250  |

| 0.425       | 1     | 0.045288085938   | 0.19653320312500  | 0.731079101563  |

| 0.0         | 0     |                  | 0.250000000000000 | 0.5000000000000 |

Figure 13: The Block Diagram for a Taylor Series Implementation of the Sigmoid.

Figure 14: VHDL Approximation. The VHDL implementation of the Taylor series squash is on the left and the error is shown on the right. The approximation of the sigmoid remains within .005 for the entire range.

Figure 15: Comparison of FPGA Output with Real Output. One of the known input/output relationships was used to test the FPGA implementation. The image map on the left was produced by the FPGA and the image map on the right was produced by the original neural network.

#### Comparison Summary

Table 4 is a comparison of the different implementations, showing the amount of chip assets necessary, latency and error for each implementation. The average pixel error was found using a computer simulation holding all other calculations at maximum accuracy and using the approximation in place of the sigmoid.

TABLE 4

A COMPARISON OF APPROXIMATIONS

| Implementation       | Slices | Memory  | Multipliers | Latency | Average Pixel Error |

|----------------------|--------|---------|-------------|---------|---------------------|

| Lookup Table         | 1951   | 2kbytes | 0           | 3       | 0.4015              |

| Shift-add            | 2026   | 0       | 0           | 5       | 1.3281              |

| CORDIC               | 3475   | 0       | 0           | 50      | 0.4279              |

| <b>Taylor Series</b> | 2085   | 0       | 3           | 10      | 0.4306              |

For our problem, fast weight access requires storage in on-chip memory and multipliers also limit the amount of memory available. This makes memory limited and the lookup table approach infeasible. However, given a smaller network or more resources, a lookup table implementation would be ideal.

The shift and add implementation is small with a low latency and uses no predefined logic for its implementation. However, it has the worst error, three times that of any other implementation. It also has no method for improvement.

The CORDIC version has the lowest error, though is significantly larger than the other four versions. This version also has a very long latency, which, in a four layer network, would add 200 clock cycles versus the next slowest 40. However, error improvement is easily done by adding more stages and can be done as long as chip area is available.

The Taylor series approximation has the third best error of four implementations, though is not much worse than the smallest error. The small improvement in latency that would be gained by using the shift-add implementation is outweighed by the increase in error and the cost of a piece-wise approximation. The desire for speed also outweighs the small error improvement that would be gained by switching to a CORDIC

implementation. In the end, we are proceeding with this network implementation using a Taylor series approximation. The actual average error resulting from the Taylor series implementation in hardware is 1.4230 units per pixel.

#### **CHAPTER FIVE**

## **Neural Network Implementations**

For this problem, several different implementation structures were used. Initially a simple design was used to test the ability of the FPGA to calculate the neural network as well as to become comfortable with the programming environment. Next, a few similar versions of the initial design were implemented in order to increase the speed of the forward computation. Finally, a completely different approach was taken to achieve the current speed up.

#### Serial Implementation

The first implementation performed all network calculations serially. Three on-board memory banks were used. One of the memory banks held the network weights with one weight per memory location. Since the inputs for the next layer are written while the current layer inputs are being read, two banks must be used to hold layer inputs. One multiplier and one accumulator are used to calculate the sum of products input to a node. The inputs from one bank and the weights are used as the inputs to the multiplier. The products are then summed by the accumulator until a node sum is completed. Then the result of the node is squashed and the result stored in the other input bank. While result is being squashed, the accumulator is cleared and the calculations for the next node begin. Once a layer is complete, the newly calculated input bank is used for the multiplier inputs while the other input bank is written over for the next layer's inputs.

For the final layer, the squash is bypassed and outputs are taken directly from the accumulator. A block diagram for the serial implementation is shown in Figure 16.

Since the serial implementation can perform one input-weight multiply per clock, the number of clocks required is equivalent the number of weights plus the latency of the squashing implementation. Since the number of weights is much greater than the latency, calculation time can be considered to be approximately the number of weights. The acoustic network contains approximately ninety-two thousand weights. This takes approximately ninety-two thousand clocks for a forward evaluation or, at one hundred megahertz, just under one millisecond.

Figure 16: The Block Diagram for the Serial Implementation of a Neural Network

## Parallel Node Implementation

One method to speed up the implementation is to calculate more than one node at a time. The structure for each node is identical to the serial implementation. However, several nodes for the next layer are calculated in parallel, decreasing computation time.

In order to calculate multiple nodes in parallel, several weights must be accessed at the same time. For the initial node parallel implementation, four nodes are calculated at a time, requiring four weights per clock. To do this, four sixteen-bit weights are stored in the sixty-four bit memory in the on board banks. Then, on each clock, four multiply and accumulators multiply an input by four different weights and find the sum of products for four nodes. As with the serial version, two banks are used for reading and writing inputs, and the accumulators are cleared when the calculations for new nodes began.

For the four node parallel version, it would seem that four squashing functions would be needed. However, the since inputs are retrieved at a rate of one per clock from the memory banks, they must also be written to at a rate of one per clock. To achieve this, while one node-sum begins a squash, the other three are stored in registers. Since the squashing function is pipelined, the other three are squashed in order, directly following the first. This allows the four node outputs to leave the pipeline serially where they are written directly to an input bank.

At most, this method could speed up the forward computation time of a neural network by a factor of four. However, not all layers have node multiples of four, so a few of the parallel node calculations are wasted calculating nonexistent nodes. The weights for the nonexistent nodes are filled with zeros. For the approximately ninety-two thousand weight neural network, the time for one forward evaluation at one hundred megahertz is roughly .25 milliseconds. A block diagram for the parallel node implementation for four nodes is shown in Figure 17.

Figure 17: The Parallel Node Implementation with Four Parallel Nodes.

A variation on this method was also implemented in order to achieve even greater speed up. The SRC-6e has six on-board memory banks. The input storage requires the use of two of the banks, leaving four banks of weight storage. Since each bank can hold four weights per memory location, a maximum of sixteen weights can be retrieved per clock cycle. This limits this implementation a maximum sixteen parallel multiplications.

If the four node parallel implementation is simply extended out to sixteen, many multiplies are wasted. To calculate a layer of fifty nodes, for example, in the last set of sixteen nodes, the final fourteen nodes are unnecessary. In order to avoid this waste, only four nodes are calculated at in parallel; however, four multiplications per node are also computed, using all sixteen available weights. Then the four products are summed and stored in an accumulator, allowing nodes to be calculated four times as quickly. Then the number of non-existent node calculations at the end of a layer is equivalent to that of the previous implementation.

In order to use four weights per node, four inputs must also be used per clock. Since sixteen bit inputs are stored in a sixty-four bit bank, four are stored in each memory address and are accessible every clock. Four squashed outputs must also be stored at the same time for use as future inputs. Instead of shifting data into one squashing function, four squashing functions are implemented in parallel. Then after node multiplications and accumulations are completed, all four nodes are squashed and the results are available at the same time for storage.

This method is nearly sixteen times faster than the serial implementation. At one hundred megahertz, the time for a forward calculation of the ninety-two thousand weight network is approximately sixty microseconds. A simplified block diagram for the implementation with sixteen multiplications in parallel is shown in Figure 18.

Figure 18: Parallel Node Implementation with Sixteen Multiplies

## Parallel Input Implementation

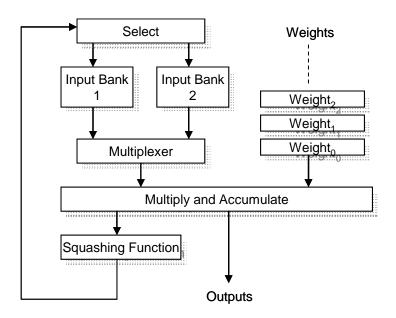

By storing weights and inputs in on-chip BRAM, many more weights can be accessed at a time as well as an entire layer of inputs. This allows many calculations to be performed in parallel, giving a significant speed increase over a serial computer.

The parallel input implementation performs all the multiplications for the calculation of one node at the same time. The previous layers outputs are multiplied by the corresponding weights for the current node. While the products are being summed, the next node's weights are multiplied by the same set of outputs, creating an efficient pipeline. However, since all the node outputs are required for calculations in the next layer, the pipeline must wait several clocks for the previous layer to finish before continuing with the next.

In order to simplify the implementation of the network, all layers are considered to be the same size as the largest, in this case, 70 nodes. Weights beyond the range of small layers are set to zero. The number of nodes calculated is controlled in order to minimize the amount of filler zero weights used. A block diagram of the node parallel calculation is shown in Figure 19. Pseudo code for control is shown below:

Multiply all inputs by all current weights

Sum all the products

Squash the sum

Save the squashed sum in output memory

Increment weight counter

Increment output counter

If output counter equals number of nodes on next layer

reset the output counter

write output memory over input memory

increment layer counter

This design takes 1465 clocks to complete one network evaluation or slightly less than fifteen microseconds. This allows the network to be evaluated more than sixty thousand times per second.

Figure 19: A Simplified Block Diagram of a Node Parallel Implementation.

## Conclusions on Neural Network Implementations

This example has shown that a hardware neural network can reasonably approximate a continuous neural network using limited accuracy for weights as well as an approximation of the squashing function. However, it must be noted that neural networks are approximations of an actual system. By approximating an approximation, needless noise is added. This problem could be avoided by training on a hardware implementation; in other words, set the weights by training with the limited accuracy as well as with the approximated squashing function.

The training could be completed using a random initialization of weights or by using the pre-trained network weights as a starting point. In either case, the squashing

function used could be chosen based more on speed of calculation rather than on how close the approximation is to the sigmoid. The shift-add version would probably be used due its size and speed. The shift-add implementation is only capable of piecewise linear approximations, though given the size of network, the number of linear segments is likely adequate.

The three different versions of neural networks could be useful in different situations. The serial implementation will fit into a small FPGA with only a few input pins for the three memory banks used. Then a circuit board could be created with a few RAM blocks and the FPGA. Inputs could be retrieved from analog to digital converters or other sources and outputs used by a computer or other segments of circuitry.

The parallel node implementation could be tailored for a problem that needs more speed than the serial implementation provides, though still needs a reasonably small FPGA. More connections would have to be made to access the greater number of memory banks, though outputs would be available four or sixteen times as quickly with four available at a time.

The parallel input implementation is useful in cases where maximum speed is necessary, such as in the real-time particle swarm inversion. For the forward computation, given a chip with enough pins, all inputs could be clocked in at the same time and used directly as the first layer inputs. Outputs, however, are still required to be received sequentially, as they are calculated sequentially.

#### **CHAPTER SIX**

## Particle Swarm Implementation

The particle swarm update equations consist of simple multiplications and additions, easily implemented on a XC2V6000. Setting the bias coefficients to powers of two and using shifts in place of multipliers further simplifies the implementation. The computation time for a hardware particle swarm optimization is solely dependent on the computation time of the fitness function. The position and velocity of one agent can be updated while the fitness of another agent is being calculated. Since the fitness function takes orders of magnitude longer to calculate, the update hardware will be inactive for a large majority of the time.

The more complicated part of the update equations is the randomness associated with the velocity update. For this implementation, we examined three different methods for implementing the randomness. For comparison, a standard particle swarm was run on a conventional computer. The average error over one hundred trials between desired output and that calculated using the found input was 1.9385 units per pixel.

### Deterministic Particle Swarm

The first method to implement randomness was simply to ignore it. Randomness was previously successfully removed to prove the stability of the algorithm [15]. Removing randomness would simplify the implementation of the particle swarm update equations. In order to estimate the effectiveness, randomness was removed from particle swarm on a conventional computer. The bias coefficients were also decreased so that the

average bias would be the same. Both the random and the deterministic particle swarms were run for ten thousand iterations for thirty searches. The global best fitness was plotted for each run as well as the average of all swarms. The plot is shown in Figure 20. For our problem, it initially appeared that including the randomness would significantly increase the success of the swarm.

Figure 20: Particle Swarm with and without Randomness. Random and deterministic particle swarms were run for ten thousand iterations thirty times. The crosses are the global best results from the deterministic particle swarm and the top line the average. The circles are the global best results from the particle swarm with randomness and the bottom line the average. The randomness significantly improves the result of particle swarm.

The deterministic particle swarm update equations lend themselves to a parallel hardware implementation since the velocity and position can be calculated at the same time. The update equations are implemented in a pipeline and one dimension can be updated on every clock cycle. The block diagram for the hardware implementation is

shown in Figure 21. The average error over one hundred trials between the desired output and that calculated using the found input was 2.3587 units per pixel.

Figure 21: Deterministic Particle Swarm Block Diagram.

#### Randomization

In order to implement randomness, a function is implemented that generated two pseudorandom numbers per clock. Two stages are added to the update pipeline to multiply the personal bias and global bias by the generated numbers.

## Linear Feedback Shift Register

One method of generating pseudorandom numbers is to use a linear feedback shift register. This method is typically used in testing digital logic designs. The Fibonacci implementation begins with an initial seed value loaded into a shift register. The value is then shifted one bit with the carry in bit determined by a logical combination of the bits in the previous value [16].

Prior to implementation, the quality of the randomness of the method was tested in computer simulations. Ideally, the probability of an output of a uniform random would

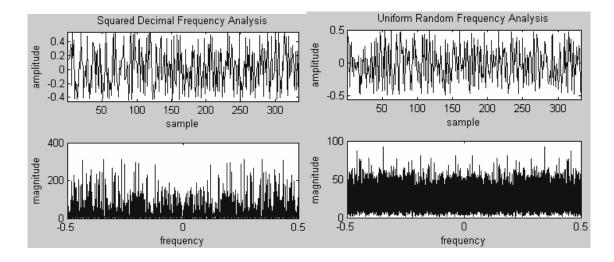

be equal for all values with in the specified range. Figure 22 shows the histogram of ten thousand outputs from an LFSR as well as that of the uniform random number generator from a computer simulation. The LFSR result appears to slightly favor values in the extremes, while the computer simulation generator appears to be uniform throughout. At this point, the LFSR appears to be a suitable uniform random number generator.

The second requirement to be an acceptable uniform random number generator is that one output should not be related to other outputs. A good method to verify this is that the frequencies present in a stream of unrelated outputs is uniform. Figure 23 shows the frequencies present in the LFSR and in the computer simulation generator as well as short segment of the stream. As expected, the computer simulation generator has all frequencies present at fairly equal strengths. The LFSR, however, has predominately low frequencies, indicating that adjacent outputs are highly related to each other. This is apparent from looking at the output streams. The computer simulation generator varies greatly between samples while the LFSR output follows a curved pattern. This indicates that the linear feedback shift register does not make a very good uniform random number generator.

Even though it is not a perfect random number generator, the linear feedback shift register was implemented into the particle swarm. For sixteen bits of randomness, the last sixteen bits are taken from a twenty-one bit LFSR. The average error over one hundred trials between the desired output and that calculated using the found input was 2.3522 units per pixel.

Figure 22: Histograms for a LFSR Implementation and a Uniform Random Variable.

Figure 23: Output Streams and Frequency Spectra f or a LFSR Implementation and a Uniform Random Variable.

## Squared Decimal Implementation

A second method of generating pseudorandom numbers was based on the pi to the fifth method. It is possible to create a stream of apparently random numbers by adding a decimal number to pi and then taking the sum to the fifth power. The fractional portion of the result is the pseudorandom number and used as the next number added to pi. This method is not specific to pi or to the fifth power. The hardware implementation uses a squared power and a one followed seventeen randomly assigned fractional bits in place of pi.

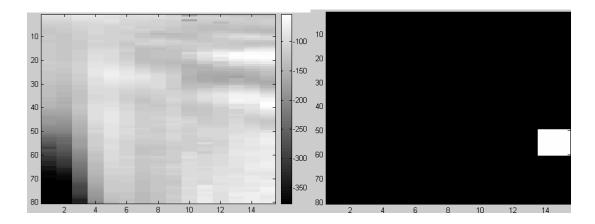

As with the linear feedback shift register, the quality of the randomness was tested in computer simulations and compared with that of the computer simulation uniform random variable generator. From the histogram shown in Figure 24, the squared decimal random generator is not uniform in nature and appears to have a tendency towards smaller numbers. In this aspect, it is worse than the linear feedback shift register implementation. However, in the frequency spectrum shown in Figure 25, the squared decimal implementation is more uniform. This manifests itself in the output stream, which contains no obvious patterns. In this aspect the squared decimal implementation is closer to being more random between samples than the LFSR.

As with the LFSR, the squared decimal implementation was generated in hardware and used in the particle swarm search. The average error over one hundred trials between the desired output and that calculated using the found input was 2.3694 units per pixel.

Figure 24: Histograms for a Squared Decimal Implementation and a Uniform Random Variable.

Figure 25: Output Streams and Frequency Spectra f or a Squared Decimal Implementation and a Uniform Random Variable.

#### Particle Swarm Randomness Results

When searching for a known achievable set, all three methods of particle swarm implementation produced approximately the same levels of output error, making the deterministic method most desirable. In actuality, the deterministic method does introduce some randomness due to truncation during the shifting of biases. It was also noted that none of the implementation methods were as accurate as the conventional computer average error of 1.9385 units per pixel.

In order to account for this increase, it was noted that the hardware implementation was not searching using an identical network to the computer. Therefore, a more accurate comparison can be made using output from the hardware neural network given the found inputs. Comparing to the hardware output, the average pixel error for the deterministic method was 1.8055 units per pixel, actually better than the conventional swarm. The average pixel error of 1.4230 between the computer network outputs and hardware network outputs combined with the search error gave rise to the overall higher error.

The average pixel error between the computer network outputs and the acoustic model outputs that it is mimicking is 4.5801 units per pixel. With this level of error already in the system, the extra .5 units of error caused by the network and particle swarm translation to hardware were deemed to be insignificant.

## Conclusions on Particle Swarm Implementation

The output from the hardware particle swarm inversion has an average pixel difference of 2.5387 from a known achievable desired output or an average difference of

1.53%. This low error implies that the particle swarm inversion will be able to find a set of inputs that produces outputs closest or near the closest to a desired output set.

Figure 26 and Figure 27 show two sets of outputs from inputs found for the maximization of a specific area as well as the specified area. All other areas were ignored for calculation of fitness. Localized maximization is equivalent to attempting to find infinite ensonification, which, of course, is outside the achievable set. It is evident from the figures that the particle swarm optimization found a set of inputs which maximizes the local area and ignores the rest of the figure.

The time to complete the same one hundred thousand iteration particle swarm optimization on a conventional computer is nearly two minutes. At one hundred megahertz, the two-chip hardware implementation takes under 1.8 seconds to complete and is approximately sixty-five times faster.

Figure 26: Particle Swarm Results Maximizing a Specified Area. The white area in the image on the right shows the desired maximization area. The image on the left shows the outputs from the solution found by the particle swarm.

Figure 27: Particle Swarm Results Maximizing a Specified Area. The white area in the image on the right shows the desired maximization area. The image on the left shows the outputs from the solution found by the particle swarm.

#### **CHAPTER SEVEN**

# Algorithm Speedup through FPGA Implementation

High-end consumer computers have processors operating at speeds greater than three gigahertz and cost less than a few thousand dollars. FPGAs, however, typically run no faster than a few hundred megahertz and can cost several thousand dollars per chip. For certain algorithms the time saved by the ability to perform computations in parallel is lost from the slower clock speed of the FPGA. Other factors that determine algorithm calculation time include the ability for an algorithm to be pipelined and the speed at which memory can be accessed.

#### Parallel-able

Algorithms which perform many independent calculations are typically prime candidates for FPGA implementation. The calculations can be performed in parallel by the FPGA, whereas in a conventional computer they are performed serially. The increase in algebraic calculations per clock can provide a large speedup over a serial computer operating at the same rate. For the neural network example, many thousands of independent calculations are performed, making it a strong candidate for hardware implementation. On the output layer, around seventy thousand multiplications could be preformed in parallel, given the appropriate hardware.

The maximum speedup for an algorithm can be found by dividing the total number of computations by the length of the largest dependent set or the largest set of computations that cannot be performed in parallel. Speedup is considered to be the

number of clocks required if one calculation is performed at a time divided by the number of clocks actually used.

The largest dependent set in a neural network is directly related to the number of layers. For each layer, a multiply, a sum, and a squash must be performed before calculations for the next layer can begin. A multiplication requires two clock cycles and using an ideal lookup table, a squash requires one clock cycle. Only a limited number of terms can be summed in a clock cycle, so the number of clock cycles required is logarithmically related to the number of terms in the layer. For the example neural network and hardware, only five terms can be summed per clock to achieve timing. Therefore, the sum for each layer takes three clock cycles to complete. Each layer needs six clock cycles to complete, except for the output layer which only needs five. With three hidden layer calculations and one output layer calculation, the longest set of dependent calculations is twenty-three.

The required calculations are approximately ninety thousand multiplies, ninety thousand additions, and one hundred and sixty squashes. This combines for a total number of serial clocks of about one hundred eighty thousand. This results in a maximum speed up from parallel-ability of about eight thousand.

However, the maximum speedup is not possible due to hardware constraints, so the real speedup due to parallel-ability is considered to be the total number of calculations divided by the longest length of dependent calculations multiplied by the number of times the calculations are repeated. For the first three layers, the longest dependent set is twenty-five and this repeated one hundred sixty times. For the final layer, the longest

dependent set is ten and is repeated one thousand two hundred times. This gives an actual speedup due to parallel-ability of about eleven.

The particle swarm update is an example of another algorithm which can achieve speedup through parallel-ability. With the above example, all twenty-seven dimensions could be updated simultaneously. Internal to each update, an additional speed up of three is achievable through performing calculations in parallel. This gives a total speed up of eighty-one.

The CORDIC algorithm, however, does not achieve much gain from parallel-ability. The CORDIC rotation calculations are all related and require a serial implementation. With each rotation dependent on the previous, the only parallel gain is from the three algebraic computations for a rotation. The Taylor series and shift-add approximations are two other examples in which limited gain is made from parallel-ability.

## Pipeline-able

Even if an algorithm does not have many unrelated calculations, it is still possible for an implementation to be advantageous if the algorithm is pipeline-able. The maximum speedup achievable from pipelining is the length of the longest set of calculations that cannot be performed in parallel. The total maximum speedup is the speedup from parallel-ability multiplied by the speed up from pipelining. This gives maximum speedup equal to the number of calculations in an algorithm.

The CORDIC algorithm, for example, is pipeline-able, and this is especially useful if many stages of the algorithm are used. In the pipeline, many calculations are performed at the same time; however, each is for a different input. Then, total speedup is

not only the three calculations performed in parallel, but also the length of the pipeline used. A ten stage CORDIC algorithm would perform three calculations in parallel multiplied by ten stages in the pipeline, or thirty calculations per clock. This speedup makes a one hundred megahertz FPGA competitive with a three gigahertz serial computer operating at one calculation per clock.

This maximum speed up cannot actually be achieved. However, it is approached as the number of the CORDIC computations needed to be performed increases. If only a few computations are required, the full speedup effect is not appreciated due to the extra clocks from the latency when waiting for the last computation to be completed. The real amount of speed up is

$$S_a = S_m \left( \frac{N}{N + L - 1} \right)$$

Where  $S_a$  is the actual speedup,  $S_m$  is the maximum speedup, N is the number of computations to be performed and L is the latency of the pipeline. In the pipelined CORDIC algorithm, if only one computation is required and the pipeline is ten stages, then the actual speedup is only three. As expected, this is the same as that found when examining parallel-ability.

Some algorithms, such as the neural network, are unable to be fully pipelined due to hardware limitations. Given enough hardware, a neural network would be able to be pipelined to perform all multiplications, additions and sigmoid calculations simultaneously. In the case of the example neural network, the gain would be the combination of the gains for the multiplications, additions and squashing functions, or for a total of around one hundred.

However, it is not possible to perform all calculations at one time and hardware must be reused, making it impossible to achieve one evaluation per clock. A pipeline gain is still achieved with the calculation of individual nodes. The squashed sum of each node for a layer can be treated as different computations and a pipeline made evaluating one node per clock.

For each layer, the above speed up equation holds with N set to the number of nodes and L set to the latency of calculating one node. The maximum speedup changes from layer to layer due to the different number of multiplies between layers as well as the latency that is required because one layer must finish before another begins. The average speedup per node due to pipeline-ability is approximately eleven. The pipeline speedup combined with the parallel speedup gives a total speed up of one hundred and twenty-one. This is equivalent to the one hundred and eighty thousand serial clocks needed divided by the clocks necessary to complete one forward evaluation.

## Memory Transfer

Another important factor in considering the usefulness of an FPGA implementation is the memory transfer that occurs. To use an FPGA algorithm, the microprocessors in the SRC-6e must first retrieve data from main memory and then load it into the on-board memory banks. If the algorithm was performed directly in the microprocessors, the data is only needed to be retrieved from memory, at which point it can remain in cache to be reused. The extra time of transferring data to and from the on-board memory banks can make a hardware implementation slower than that in a microprocessor.

The CORDIC example is one case. With a ten stage CORDIC pipeline, the speedup is thirty. This makes a one hundred megahertz hardware implementation as fast as a three gigahertz serial processor. However, if data is stored and retrieved in the onboard memory with a one hundred megahertz processor, an extra two clocks per calculation is needed, taking the time per calculation from one clock to three. This is a slowdown by three, making the net speedup only ten. This makes the CORDIC implementation only competitive with a one gigahertz serial computer. For any fully pipelined implementation, the speedup decreases by three.

The neural network speed is impacted less by data transfer. This is, however, partly due to the large number of clocks used to calculate a forward evaluation. Only twenty-seven inputs are transferred to the on-board memory and twelve hundred outputs are transferred out. This increases the clocks used from 1465 to 2837, or a slowdown of about 1.93. This takes the net speedup from 123 to about 64.

Particle swarm is hurt the least by data transfer. It takes about one hundred and fifty million clocks to complete. The only data transferred is the twelve hundred desired outputs and the twenty seven found inputs. This is a slowdown of well under one percent and can be considered negligible.

## Speed Ratio

In the end, all three of the above factors must be considered when considering whether or not to implement an algorithm in hardware. Typically rough estimates of speedups for parallel-ability and pipeline-ability and the slowdown from data transfer are accurate enough to determine whether an algorithm will be more efficient in a hardware implementation or in a faster dedicated serial processor. If estimates are not accurate

enough to confidently say which will be faster, programming both and comparing actual times is probably unnecessary. Given the choice between a hardware implementation and a possibly slightly slower microprocessor program, the extra cost saved by using the microprocessor will likely balance any speed gain.

#### **Conclusions**

For the neural network implementation, several approximations were made in both the data representation and in algorithm calculations in order to accommodate the hardware limitations of the FPGA as well as to decrease calculation time. The error added by the translation to a sixteen-bit fixed point representation proved to be insignificant. Error from approximating the squashing function also showed to be insignificant. After examining various implementations, a Taylor Series approximation was used for the final network implementation.

Once approximations were proven to be feasible, various possibilities of network implementations were examined. The parallel input network implementation was able to achieve significant speedup through both parallel-ability and pipeline-ability; therefore, this implementation was used for the particle swarm inversion.

The particle swarm inversion was able to achieve speedup through parallel-ability, since its calculations could be performed during fitness evaluations. Randomness was removed from the particle swarm update equations since it added complexity to the implementation and minimal improvement to the results. The overall speedup of particle swarm inversion of neural networks was enough to take the algorithm calculation time from several minutes on a conventional computer to less than a few seconds.

**APPENDICES**

#### APPENDIX A

# Parallel Input Network and Swarm Code

#### Main.c

```

#include <sys/types.h>

#include <stdio.h>

#include <stdlib.h>

#include libmap.h>

#include <math.h>

void swarm();

int main() {

/*these are all the weights

weights are stored in 16 bit fixed point with 4 weights per 64 bit int

Fixed point for input layer is one sign bit followed by 15 fractional bits S.XXX

XXXX XXXX XXXX

Fixed point for middle layers is one sign bit followed by 7 integer bits and 8

fractional bits S XXX XXXX.XXXX XXXX

Fixed point for output layers is one sign bit followed by 10 integer bits and 5

fractional bits S XXX XXXX XXXXX XXXX*/

uint64_t weights[24480] = {

0xfae3f80000080891,

0x0002ea04fffcff4d,

0xff9b06be0a34f634.

0xf7f309590b59ff97,

0x1918137b0e4b0966,

0x0ef20405fdc2f099,

0xdff2e041cb566079,

//not all numbers are shown to reduced code length

0xec6cf33bfdb2fe01,

0x002a0171fe100143.

0xfea904e4006efc26,

0x002e008501d70074,

0x01f7ff82ffde000f,

0xf5b80316d9950000};

```

```

/*This is the maximum limit of search space, 16 bits fixed point

Sign bit followed by 14 integer bits and 1 fractional bit S XXX XXXX XXXX

XXX.X*/

uint64_t xMax[27] = {

364,

350,

12514,

//not all numbers are shown to reduced code length

3044.

3042};

/*This is the minimum limit of search space, 16 bits fixed point

Sign bit followed by 14 integer bits and 1 fractional bit S XXX XXXX XXXX

XXX.X*/

uint64_t xMin[27] = {

92,

92.

5152,

//not all numbers are shown to reduced code length

2972,

2980};

/*This is the maximum velocity of particles, 16 bits fixed point

Sign bit followed by 14 integer bits and 1 fractional bit S XXX XXXX XXXX

XXX.X*/

uint64_t vMax[27] = {

54.

52,

//not all numbers are shown to reduced code length

14,

12};

/*This is the starting locations of 10 search agents. 16 bits fixed point. Sign bit

followed by 14 integer bits and 1 fractional bit S XXX XXXX XXXX XXXX XXXX.X*/

uint64_t psuedorandx[270] = {

364,

350.

//not all numbers are shown to reduced code length

2992.

2987};

/*This is the starting velocities of ten search agents, 16 bits fixed point

Sign bit followed by 14 integer bits and 1 fractional bit S XXX XXXX XXXX

XXX.X*/

uint64_t psuedorandv[270] ={

```

```

65534,

65534,

//not all numbers are shown to reduced code length

65534};

/*variable allocation, uses discussed further later*/

uint64_t *WEIGHTS;

uint64_t *Agents;

uint64_t *limits;

uint64_t *desired;

uint64_t *bestout;

double starttime, endtime, cumetime; //time variables

extern double second(); //time variables

int knownouts[1200];

int mapnum = 0;

int i,n,j;

int x1,y1,x2,y2;

int answer;

FILE *knownfile;

//allocate the map

map_allocate(1);

/*make space in memory for variables*/

WEIGHTS = (uint64_t *)Cache_Aligned_Allocate(24480 * 8);

Agents = (uint64_t *)Cache_Aligned_Allocate(272 * 8);

limits = (uint64 t *)Cache Aligned Allocate(28 * 8);

desired = (uint64_t *)Cache_Aligned_Allocate(1200 * 8);

bestout = (uint64_t *)Cache_Aligned_Allocate(28 * 8);

/*assign the weights to aligned memory for transfer to chip banks*/

for (i=0; i<24480; i++)

WEIGHTS[i] = weights[i];

}

/*This variable is stored after the limits and it is a flag that

controls the loading of weights. 1 is load weights on function call*/

\lim_{x \to 0} [27] = 1;

/*A call to the chip, the only purpose of this call is to load the weights*/

swarm(WEIGHTS, Agents, limits, desired, bestout, mapnum);

```

```

/*This variable is stored after the limits and it is a flag that

controls the loading of weights. 0 does not load weights*/

\lim_{x \to 0} [27] = 0;

/*this puts the xMax, xMin, and vMax 16 bit variables into a 64 bit variable to

simplfy transfers to chip*/

uint64_t temp1,temp2,temp3;

for(i=0; i<27; i++)

temp1 = xMax[i] \ll 32;

temp2 = xMin[i] \ll 16;

temp3 = vMax[i];

limits[i] = temp1 + temp2 + temp3;

}

/*this puts the starting velocity and position 16 bit variables into a 64 bit variable

to simplfy transfers to chip*/

for(i=0; i<10; i++)

for(j=0; j<27; j++)

temp1 = psuedorandv[i+27*i] << 16;

temp2 = psuedorandx[j+27*i];

Agents[j*10+i]= temp1 + temp2;

}

}

/*Query user to determine type of search desired or to quit*/

answer = 4;

while(answer !=1 \&\& answer !=2 \&\& answer !=3)

printf("Would like to match an output from the file knownouts.txt or

maximize a rectangle?\n");

printf("Type 1 for known set or 2 for rectangle or 3 to quit:");

scanf("%d",&answer);

}

/*loop to keep doing multiple searches*/

while(answer !=3)

/*To maximize(get as close to 0 as possible) the ensonification in a

specified rectangle*/

if(answer == 2)

x1=100;

x2=100;

```

```

y1=100;

y2=100;

printf("Type in corners of desired square(1<=X1<=X2<=15,

1 \le Y1 \le Y2 \le 80:\n");

while(x1>15 || x1<1)

printf("X1?:");

scanf("%d",&x1);

while(x2>15 || x2< x1)

printf("X2?:");

scanf("%d",&x2);

while(y1>80 || y1<1)

printf("Y1?:");

scanf("%d",&y1);

while(y2>80 || y2<y1)

printf("Y2?:");

scanf("%d",&y2);

}

/*These loops make the desired outputs for the fitness function,

with don't care being 33568

knownouts is the desired output used by the fitness function. Note

that it is a 64 bit number.

The fitness function uses 15 bit numbers with a sign. Since all

outputs are negative, the sign

bit can be treated as a normal bit and then using 65536 can be

treated as zero.*/

for(i=0;i<1200;i++)

knownouts[i]=33568;

for(i=x1-1;i< x2;i++)

for(j=y1-1;j< y2;j++)

knownouts[i*80+j]=65536;

}

```

```

/*A known set of outputs is stored in knownouts.txt. If this option is

chosen, the set is

loaded into knownouts, the desired result of fitness function. Outputs are

16 bits with 1

sign bit followed by 10 integer bits and 5 fractional bits S XXX XXXX

XXX.X XXXX*/

else

knownfile = fopen("knownouts.txt","r");

for(i=0; i<1200; i++)

fscanf(knownfile, "%d", &knownouts[i]);

fclose(knownfile);

}

/*put the desired outputs into a variable for transfer to

the chip*/

for(i=0; i<1200; i++)

desired[i] = knownouts[i];

}

/*record starting time*/

starttime = second();

/*Call the PSO with appropriate variables*/

swarm(WEIGHTS, Agents, limits, desired, bestout, mapnum);

/*record end time and display total calculation time*/

endtime = second();

cumetime = endtime-starttime:

printf("%f seconds\n",cumetime);

/*best out is the set of inputs found the most accurately matched the